DFx, DFM, DFT for EMS

5

DFx, DFM, DFT for EMS: Design That Manufactures & Tests Well

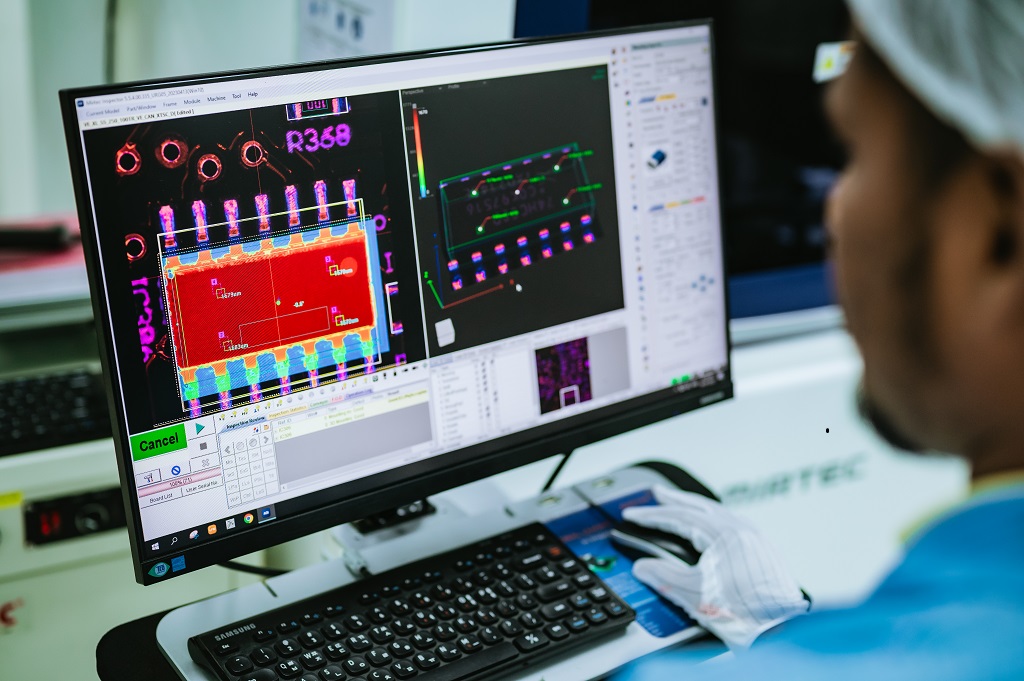

DFx/DFM/DFT decisions determine yield, speed, and auditability. INDIC designs for manufacturability and testability at the schematic/layout stage: a test-point strategy with boundary-scan JTAG, a coverage matrix across ICT/FCT/EOL,and limits tied to a golden sample. We bind results to serials through MES traceability and enforce no-pass/no-ship, so designs manufacture and test well from EVT→DVT→PVT.

Why DFx/DFT decides yield and speed

Change overs and variant growth expose weak DFx/DFT. We prevent late rework by fixing access, heat, and tolerance issues in design reviews. This raises first-pass yield (FPY) under LVHM conditions and shortens time to stable build.

DFT: test-point strategy & boundary-scan JTAG

- Test-point strategy. Reserve access on critical nets; plan isolation points; place fiducials and keepouts for reliable probing.

- Boundary-scan JTAG. Close hidden BGA interconnects where physical access is limited; pair vectors with selective ICT for analog values.

- Coverage definition. Map what ICT must detect, what FCT proves, and what EOL gates before fixtures are built.

INDIC documents this in a DFT review and converts it into a station-level coverage matrix.

DFM: stencil, land patterns, heat &mechanics

- Stencil/land patterns & paste volume for fine-pitch and 01005; verify reflow profiling windows.

- Connector clocking and keep outs for harness entry and torque tools; specify latch/strain-relief geometry.

- Panelization/depane rules to limit stress on dense, tall, or shielded assemblies.

- Thermal paths (vias, planes) to prevent hot-spots that degrade reliability or create false fails at FCT.

Golden sample, guard-band limits & first-article inspection

We lock a golden sample and derive guard-band limits for key parameters. At each recipe or fixture change, first-article inspection verifies limits and recipes before volume.

Coverage matrix across ICT/FCT/EOL with MES traceability

- ICT for opens/shorts/values and net integrity.

- Boundary-scan JTAG where access is tight.

- FCT with realistic stimuli for interfaces, sensors/actuators.

- EOL as the shipping gate (features + safety).

- OBP on-line binds firmware version/checksum to the unit serial.

- MES traceability records all station results; no-pass/no-ship blocks down stream movement

INDIC owns the coverage file, limit versions, and fixture BOM under change control.

Case evidence 1— DFT “add access, cut escapes”

A dense industrial PCBA launched without adequate access. We added test points, clarified isolation, and re-balanced the coverage split (ICT/FCT/EOL). Result: fewer late failures, reduced dependence on final test, higher FPY, and lower debug/rework cost. The board now manufactures and tests well because testability is in the layout—not bolted on later.

Case evidence 2— Fixture alignment → +7% FPY, +8% throughput

Random functional test failures traced to fixture mechanics. We added a pre-centering guide, corrected guide-pin diameter to match board tooling holes, and verified suppliers before replacing pins across fixtures. Re-test under the same limits delivered FPY +7%,throughput +8%,and eliminated intermittent failures. Mechanical tolerance is part of DFM/DFT—not just fixture craft.

What you provide; what INDIC returns

You provide: BOM/AVL, stack-ups/Gerbers or ODB++, netlists, target regulations, firmware image/checksum rules, risk priorities.

INDIC returns: a DFx/DFT report, a station-level coverage matrix (ICT/JTAG/FCT/EOL), fixture plan (reuse vs redesign), golden sample+ guard-band limits, and the MES traceability schema (fields, gates, evidence pack).

Quick DFx audit checklist (design that manufactures & tests well)

- Schematic/layout reviewed for test-point strategy and boundary-scan JTAG chains.

- Panel, fiducials, keep outs, and depane rules defined.

- Stencil/paste and reflow profiling windows documented.

- Golden sample locked; guard-band limits versioned with rollback.

- ICT/FCT/EOL responsibilities clear; evidence pack template ready.

- First-article inspection at every recipe/fixture change.

- MES traceability and OBP bound to serial; no-pass/no-ship active.

DFx, DFM, DFT for EMS: Design That Manufactures & Tests Well (ICT/FCT/EOL & JTAG Ready) - Bottom Line

Design for manufacturability and testability up front. Use a test-point strategy with boundary-scan JTAG, define ICT/FCT/EOL in a coverage matrix, and tie limits to a golden sample. Bind everything to MES traceability. That’s how designs manufacture and test well and hold FPY as variants grow.